더 얇게 만들어야 하는 HBM

단층 사이 공간 좁게 만들어야

하이브리드 본딩, 핵심 기술로

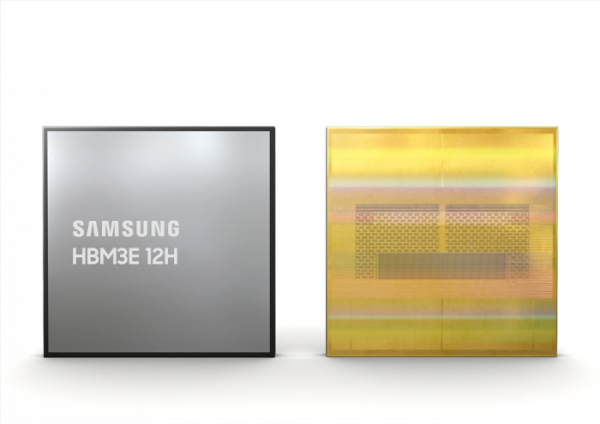

지금 인공지능(AI) 반도체 시장의 주류는 고대역폭메모리(HBM)이며, 이 가운데 최신 버전은 5세대인 HBM3E다. D램을 쌓아 올리는 방식으로 만들어진 HBM3E는 8단 중심으로 양산되고 있으나, 내년에는 12단의 비중이 크게 올라갈 것으로 보인다. HBM의 단수가 올라가면 데이터 전송 속도와 메모리 용량이 크게 늘어나지만, 기술적인 한계도 뚜렷하다. 하이브리드 본딩 등 기술력이 HBM 단수를 높이는 데에 핵심이 될 전망이다.

김운호 IBK투자증권 연구원은 “강력한 AI 수요는 내년까지 지속할 것”이라며 “내년에는 HBM 중 가장 프리미엄이 높다고 알려진 HBM3E 12단 비중이 50%에 달할 것”이라고 전망했다. SK하이닉스는 내년 중 16단 상용화 계획을 밝힌 바 있다.

HBM3E 12단은 D램을 12층으로 쌓았다는 것을 의미한다. HBM 칩의 가장 큰 고객사는 미국 엔비디아다. 엔비디아는 현재 AI 가속기인 B100과 B200, GB200 등에 HBM3E 8단을 탑재하지만, 내년부터는 B200A와 블랙웰 울트라 제품에 12단을 사용할 계획이다.

최종적으로 얼마나 많은 데이터를 한 번에 보내는 것이 HBM의 궁극적인 목적이다. D램의 층수를 쌓아 올려 데이터를 저장하는 공간을 늘리는 것이 성능을 올리기 위한 핵심 기술이다. 물론 이 공정에서 기술적인 어려움이 존재한다. 단수를 쌓으면서 발생하는 과열 문제나 각각의 칩을 연결하는 기술의 문제, 물리적 안전성 등이다.

전문가들은 HBM3E의 단을 계속 쌓기 위해선 칩의 물리적‧전기적 접합 방식과 회로 설계 기술을 안정화해야 한다고 설명했다.

D램과 D램 사이를 연결에는 작은 구슬 형태인 ‘마이크로 범프’가 사용된다. 이 범프로 생기는 두께를 더 줄이기 위해 도입된 기술이 ‘하이브리드 본딩’이다. 범프 없이 직접 연결하는 방식인데 불필요한 두께를 줄일 수 있을 것으로 기대된다.

권기원 성균관대 반도체시스템공학과 교수는 “대체로 8단이나 12단이나 결과물의 높이는 똑같이 정해지기 때문에 단수가 올라갈수록 칩은 더 얇아지고 그사이 간격도 좁아져야 한다”며 “학계에서는 하이브리드 본딩 연구를 이뤄냈고 현재 상용화 단계로 넘어가는 과정에 있다. 이 기술이 잘 적용되면 16단도 쉽게 올리 수 있다”고 말했다.

하이브리드 본딩 중 하나가 ‘코퍼 투 코퍼 본딩’ 방식이다. 반도체 칩의 배선에 구리를 입히고, 이를 직접 연결하는 기술이다. 한 대학교 반도체공학과 교수는 “그간 물리적인 본딩을 사용하던 방식에서 벗어나 코퍼 투 코퍼 본딩으로 넘어가면 집적도를 더 올릴 수 있다”고 설명했다. 삼성전자는 이 기술을 HBM4(6세대) 적용 계획을 밝힌 바 있다.

단수가 올라가며 회로 설계도 더욱 복잡해질 것으로 예상된다. 회로는 차도의 차선과 비유할 수 있다. 최대한 많은 양의 데이터를 한 번에 빠르게 전송하기 위해 64차선밖에 되지 않는 D램보다 1024차선에 달하는 HBM이 유리한 것과 비슷하다. 회로에서 신호 에러를 최소화하고 저전력 회로를 설계하는 등 효율을 높이는 것이 중요하다.

권 교수는 “많은 D램을 적층하면 신호가 지나갈 때마다 각 층이 부하를 받게 되는데, 이는 고속도로에 과속방지턱이 있는 것과 같다”며 “설계자는 어떻게 하면 과속방지턱을 낮출 수 있는지, 혹은 과속방지턱이 있어도 고속으로 달릴 수 있는 방법을 찾아낸다”고 설명했다.

HBM 제조사인 삼성전자와 SK하이닉스는 HBM 적층은 물론 다음 세대 HBM를 위해 하이브리드 본딩 등 기술을 개발 중이다. 관련 업계에서는 이 기술이 20단에서 본격적으로 적용될 것이라는 전망도 나온다.

한 반도체 업계의 관계자는 “단수를 올릴수록 당연히 관련 기술력이나 안정성을 올려야 하지만, 세대를 넘어가면 완전히 또 다른 요소를 담은 새로운 칩이 만들어지는 것”이라고 말했다.

![2024년을 휩쓴 밈 총정리…“올해 나는 얼마나 한국인이었나?” [해시태그]](https://img.etoday.co.kr/crop/140/88/2119590.jpg)

![‘퇴직연금 실물이전’ 서비스로 수익률 높은 금융사로 갈아탈까 [경제한줌]](https://img.etoday.co.kr/crop/140/88/2119547.jpg)

![2024년을 휩쓴 밈 총정리…“올해 나는 얼마나 한국인이었나?” [해시태그]](https://img.etoday.co.kr/crop/300/170/2119590.jpg)

![이투데이 독자편집위원회 3기 마지막 정례회의 [포토]](https://img.etoday.co.kr/crop/300/190/2119637.jpg)